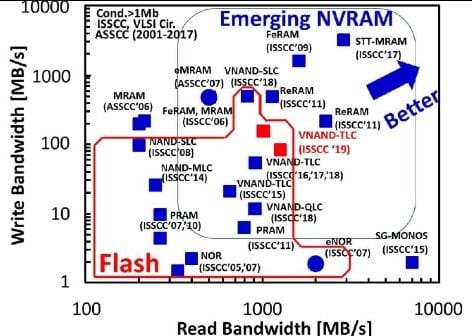

半導体の2大学会と言えばデバイス関連のIEDMと回路関連のISSCC。来年2019年のISSCCの講演内容が公表されていますがその中にもAIや5Gといったトレンドに加え、メモリ主導型のコンピューティングの話題がForumにて取り上げられています。これまでのコンピューターは基本的に「プロセッサ主導型アーキテクチャ」で構造は1940年代にノイマンが提唱したコンピューターの原型から大きくは変わっておらず、いわゆる演算装置であるプロセッサが中心にあり、そのプロセッサがI/Oを通じて入力されたデータを処理して、結果を出力するというものです。このときメモリは、プロセッサの処理を補助する一次記憶装置として、プロセッサに直接“ぶら下がる”形になっています。メモリ=DRAM,SRAMに保存されたデータは高速に読み出せるものの、記憶できる容量が小さく、電源を切ると内容が失われるため、長期保存したいデータは外部の記録装置(HDDやSSDなどのストレージ)に保存します。このシステムではデータ量が少ない場合は良いのですが大きなデータを扱うようになり、プロセッサの性能改善が停滞してくるとデータの出し入れだけで時間がかかるようになり、性能も限界が来るわけです。それに対してメモリ主導型アーキテクチャは、こうしたこれまでのプロセッサとメモリの関係を逆転させ、いわば「大きなメモリにプロセッサがぶら下がる」形の構成を取ることが特徴でHPなどがその実証に成功。このシステム自体は大まかには大容量の「共有メモリプール」を中心に配置し、すべてのデータはここに保存され、多数のプロセッサが、高速なメモリファブリックを介してメモリ上のデータにアクセスして処理するという構造。大きなデータを扱う場合も複数の計算ノードが共有メモリ上の同じデータを直接参照できるため、低速なネットワーク経由でデータをやり取りする必要がないというメリットがあります。共有メモリプールを構成するのは、電源を落としてもデータが消えない不揮発性メモリ(NVM)でHDDやSSDで構成される従来の低速なストレージを置き換えられることを前提に考えると特に大容量のデータを扱う処理が大幅に高速化することが期待できます。このシステムの構成要素として重要なのは共有される不揮発メモリとそれらをつなぐための光配線。

現時点ではこのメモリ部分を支えるものとしてはDRAMとFlashなどを組み合わせたNVDIMMとかが使われているのですが今後は速度と容量を両立した不揮発メモリが求められてくることと思います。ただ基本的にはコストや容量と速度はトレードオフなのが悩ましいところ。ただ次世代の技術として上手いバランスの取れたものが創れれば商機はあると言えますがなかなか決定打はなくNVDIMMのようなHybridなものがしばらくは主流なのかとは思います。(図はISSCCから)